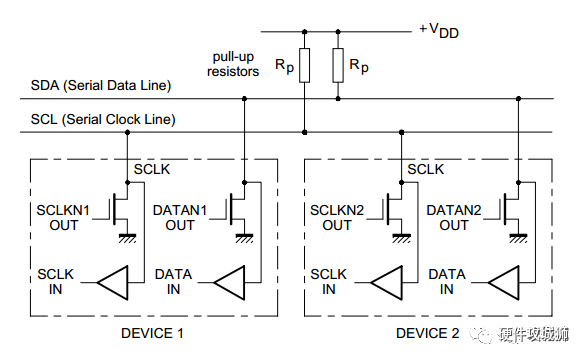

I2C一般为开漏结构,需要在外部加上拉电阻,常见的阻值有1k、1.5k、2.2k、4.7k、5.1k、10k等。

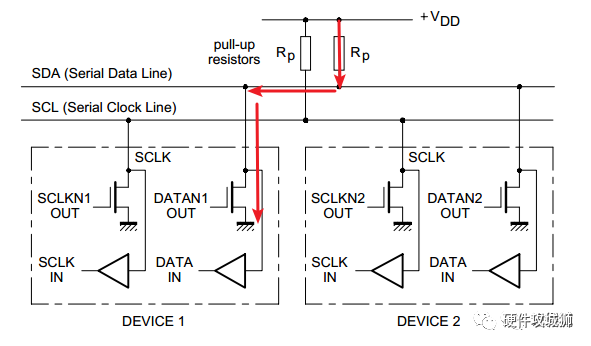

但是应该如何根据开发要求选择合适的阻值呢? 假设SDA是低电平时,即MOS管导通。那么,就可以求出上拉电阻R的阻值。

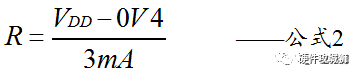

上拉电阻计算公式:

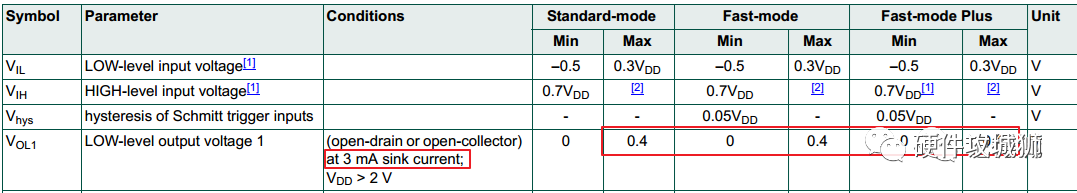

VOL定义为在漏极开路或集电极开路时,有3mA下拉电流时的低电平输出电压。IOL就是该端口的灌电流,即IOL=3mA。 由上式可得,当VDD不变, VOL取最大值时,上拉电阻有最小值。

根据I2C协议,端口输出低电平的最高允许电压是0.4V。 公式1可以改为:

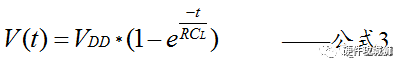

由式2可以得出:电源电压决定了上拉电阻的最小值。因此,当VDD=5V时,最小上拉电阻约为1.5k;当VDD=3V3时,约为1k。 由于I2C总线端口的高电平是通过上拉电阻实现,线上的电平从低变高时,电源通过上拉电阻对线上负载电容CL充电,这需要一定的上升时间。 电容充电一般公式:

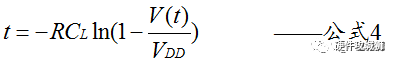

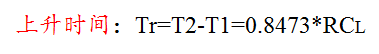

整理可得:

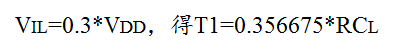

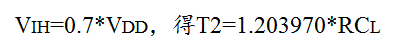

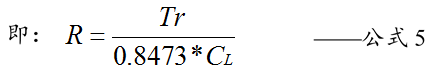

I2C规范将低于VIL或0.3VDD的电压定义为逻辑低电平,同样将高于VIH或0.7VDD的电压定义为逻辑高电平,由式4可以求得:

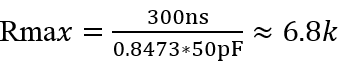

由公式5可判断,当Tr取最大值,CL取最小值时,R有最大值。 由于不同模式下,上升沿的最大时间及总线负载最大容限要求不同,标准模式、快速模式、高速模式分别是:1000ns/400pF、300ns/400pF、120ns/550pF。 以快速模式下,负载电容50pF为例,则有:

结论:电源电压决定上拉电阻的最小值,总线负载电容决定上拉电阻的最大值。

编辑:黄飞