纸币清分是银行的一项重要业务。 目前,国内很多银行使用的纸币清分机都是由国外进口的,价格昂贵。国产纸币清分机很少,而且功能都很有限,很难满足高速实时性的要求,尤其是能够用图像处理的方法来识别纸币的纸币清分机还刚刚起步。

为此,设计了一种纸币识别系统。该系统以DSP为核心处理器,结合图像传感器CCD和复杂可编程逻辑器件CPLD,并辅以高性能的模/数转换器AD9200,进行纸币图像的采集、处理。该系统主要针对人民币第四版和第五版的5元、10元、20元、50元、100元九种纸币进行识别,利用数字图像处理技术和改进的自组织映射神经网络(SOFM)提取纸币图像的长度、宽度、方向块特征,区分纸币的面值、正反面与正反向。最终完成的系统能达到较高的识别速度和识别率。

1 硬件设计

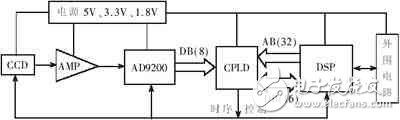

识别系统的总体硬件结构如图1所示。人民币的图像首先通过传感器CCD扫描后得到光电转换信号,并经过AMP的三倍放大;然后将放大的模拟信号经过模数转换器AD9200转换成为标准的数字信号,送入到CPLD缓存;最后通过EDMA通道输入到DSP的RAM中,在DSP中进行图像的处理和识别。整个系统的信号逻辑时序由CPLD来控制。 另外,还有一些辅助环节,如纸币输入输出装置、用户检测装置、复位装置等。

图1 识别系统的总体硬件结构框图

纸币图像的采集由CCD与A/D转换器组成。本系统采用线阵型CCD[1],它的采样速度较快、电路设计比较简单、体积小、时序也易于实现。根据系统对采集速度的要求,设置横向分辨率为4像素/毫米,共采集800个像素点;纵向的分辨率为1像素 /毫米。每张图像的高度不超过76毫米,两张纸币之间还有一定的间隔,实际采集100列。这样,每张图像的像素为800×100。纸币的进入与离开的判断使用红外线光电管检测。

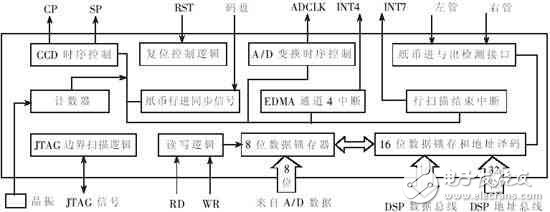

人民币的图像经过采集和A/D转换后,暂存入CPLD芯片XC95144中,然后由DSP通过EDMA通道直接传输。整个采集和存储过程的时序信号是由XC95144产生的。CPLD需要编程实现的内部结构如图2所示。其中,ADCLK信号是发送给AD9200的时钟信号,SP、CP信号传送给CCD的移位寄存器作为启动脉冲和采样时钟脉冲。

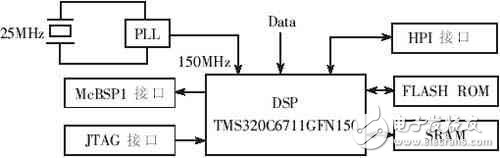

图像的识别部分由数字信号处理器DSP[2]及相应的外围电路构成,其结构如图3所示。数字信号处理器DSP选用TI公司生产的TMS320C6711GFN150芯片,主频为150MHz。扫描采集到的纸币图像数据Data经EDMA存入静态存储器SRAM中,DSP对已存入SRAM的数据作一系列的识别算法运算,并将最终结果通过DSP的McBSP1口输出。

图2 CPLD的内部结构图

图3 DSP及相应的外围电路的结构图