今天我们来看看电源完整性分析中重要的一环,去耦电容的使用。

电容实际“长什么样”

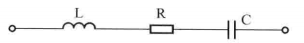

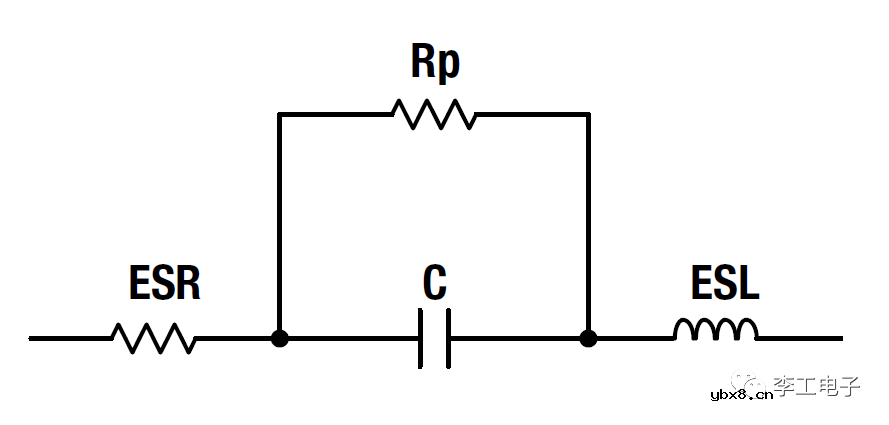

首先我们要了解一个电容的实际特性,一个真实电容可以看成下图所示的简化模型:

电容的简化模型

ESL为串联电感、ESR为串联电阻,C为理想电容。根据计算当信号频率为电容谐振频率即:

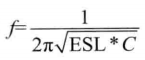

此时容抗和感抗相互抵消,电容的阻抗值最低。如下图所示:

电容的阻抗特性

图中阻抗最低点对应的频率就是电容的谐振频率22.508MHz。随着频率升高,ESR先逐渐降低,再缓慢上升。

可以说从起始频率到谐振频点之前,电容的阻抗特性以容抗为主,当频率点过谐振频点后,总的阻抗值会随频率升高而升高,电容的阻抗以感抗为主。

因此,在电容去耦设计中,当噪声频点在谐振点附近时,滤波效果最好,可以为噪声提供一条低阻抗的回路。

利用去耦电容处理电源噪声

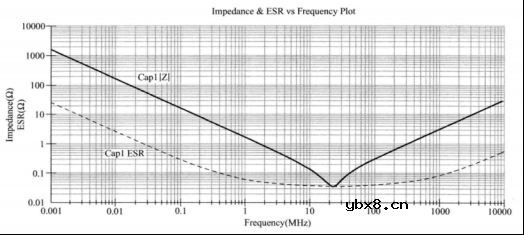

1.相同容值相同封装的电容组合:下图举例说明了其频率阻抗特性曲线,可以看到并未展宽低阻抗的频带,但是减小了谐振频点的特性阻抗。

相同容值相同封装的电容并联频率阻抗特性

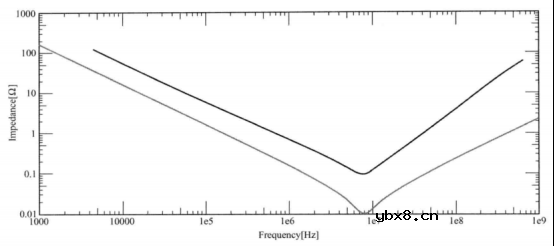

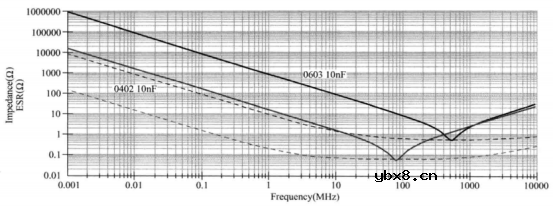

2.相同容值不同封装的电容组合:下图举例说明了其频率阻抗特性曲线,该方式会展宽低阻抗频带。

相同容值不同封装的电容并联频率阻抗特性

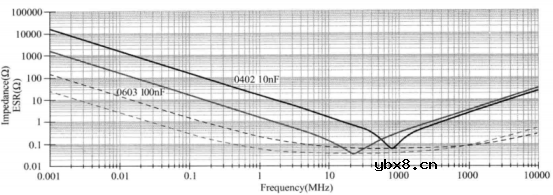

3.不同容值不同封装的电容组合:下图举例说明了其频率阻抗特性曲线,该方式可以有效地展宽低阻抗频带。

不同容值不同封装的电容并联频率阻抗特性

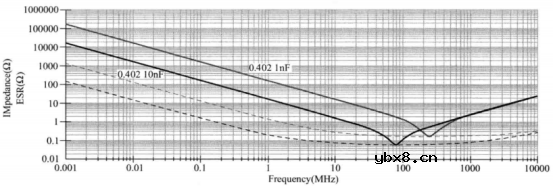

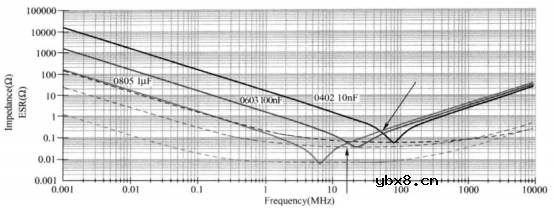

4.相同封装不同容值的电容组合:下图举例说明了其频率阻抗特性曲线,该方式可以有效地展宽低阻抗频带。

相同封装不同容值的电容并联频率阻抗特性

电容并联作为去耦电容时,需要抑制并联谐振峰的问题,如下图举例所示:

三个电容并联的频率阻抗特性曲线

3个不同的电容并联时,因电容寄生电感的影响,在某个频点处会发生并联谐振。如图中的箭头所示,3个电容的自谐振点彼此间出现2个阻抗非常高的点叫做并联谐振峰。因此,为了将电源的目标阻抗控制在一定的范围内,必须有效地抑制并联谐振峰。

作者给出了对于不同频率去耦的大概经验范围:

1.10kHz以下用VRM电源转换即可完成负载电流的实时响应;

2.10kHz~几百kHz需要用到BUCK电容(电解电容、钽电容);

3.几百kHz~100MHz,需要用小封装的小电容值的电容(如陶瓷电容);

4.大于100MHz就要靠IC的封装电容了。

审核编辑:刘清

突破人形机器人控制器性能瓶颈:高效稳定的...

突破人形机器人控制器性能瓶颈:高效稳定的...

时间:2026-03-05

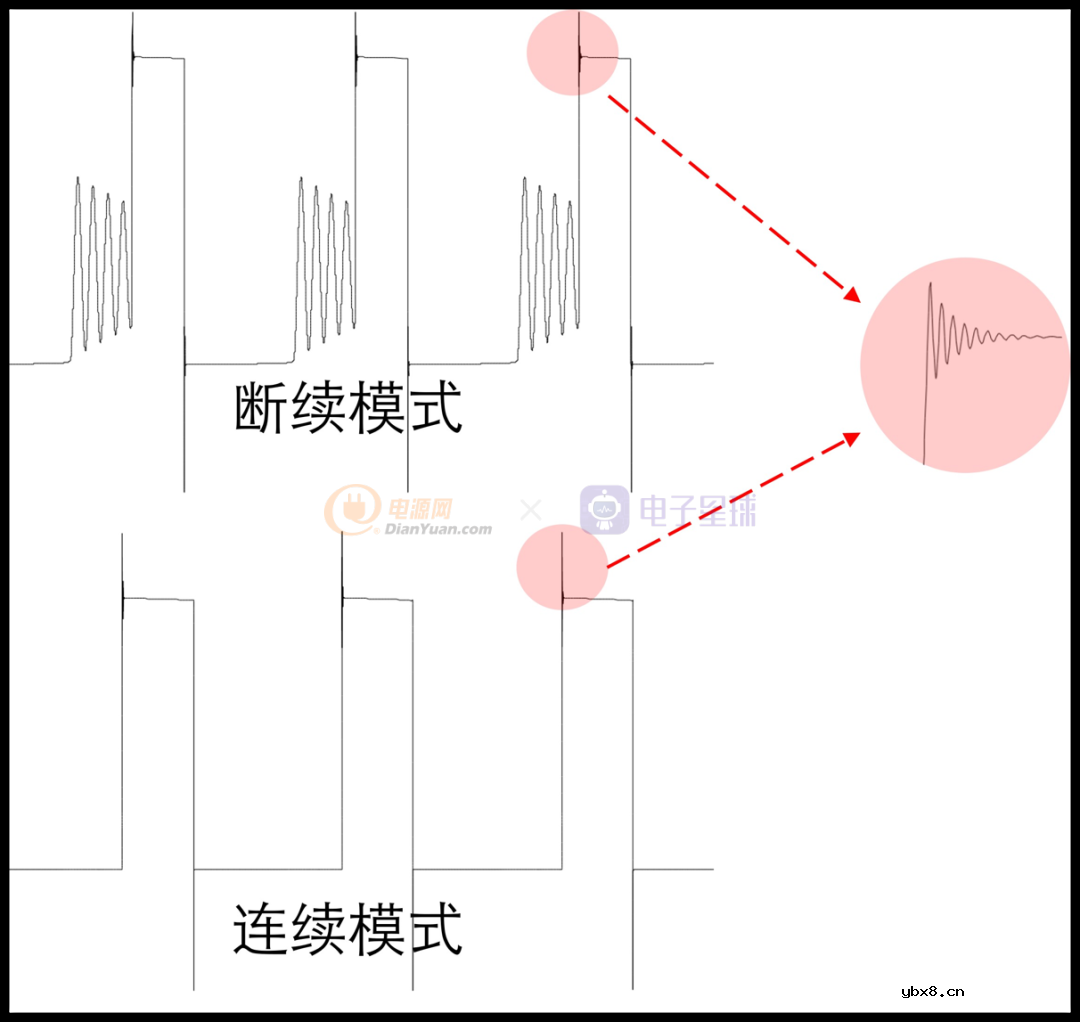

一文讲懂开关电源的阻尼振荡

一文讲懂开关电源的阻尼振荡

时间:2026-03-05

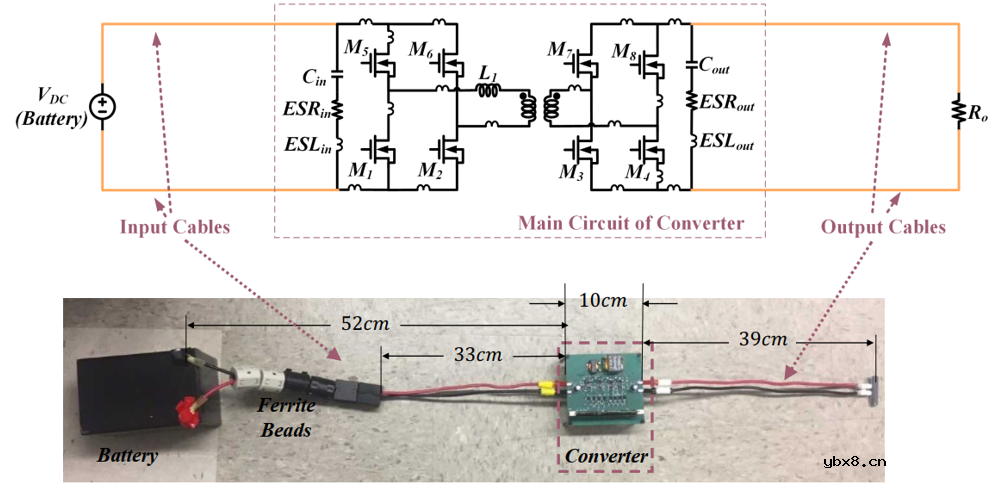

使用过滤器电容器和诱导器来抑制受辐射的EM...

使用过滤器电容器和诱导器来抑制受辐射的EM...

时间:2026-03-05

智能硬件遭遇销量困局 看社区O2O如何破解

智能硬件遭遇销量困局 看社区O2O如何破解

时间:2026-03-05

物联网新时代,关于安全的5大错误认知

物联网新时代,关于安全的5大错误认知

时间:2026-03-05

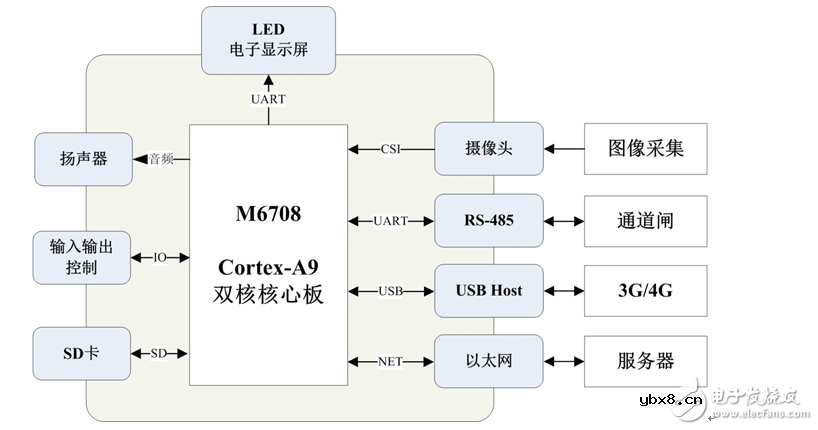

智能停车场一体化控制器方案简述

智能停车场一体化控制器方案简述

时间:2026-03-05

ZigBee应用于智能家居是否存在严重漏洞?

ZigBee应用于智能家居是否存在严重漏洞?

时间:2026-03-05

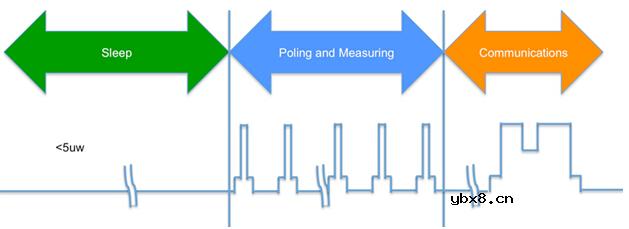

推动物联网发展,供电是基础设备的生命线

推动物联网发展,供电是基础设备的生命线

时间:2026-03-05

楼宇对讲走向标准化 四大发展方向明确

楼宇对讲走向标准化 四大发展方向明确

时间:2026-03-05

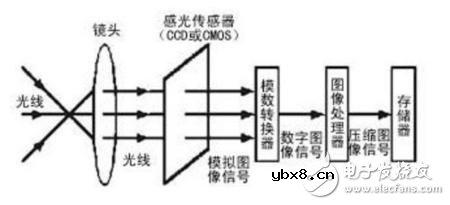

最帅“黑”科技:让普通手机可扫描3D

最帅“黑”科技:让普通手机可扫描3D

时间:2026-03-05

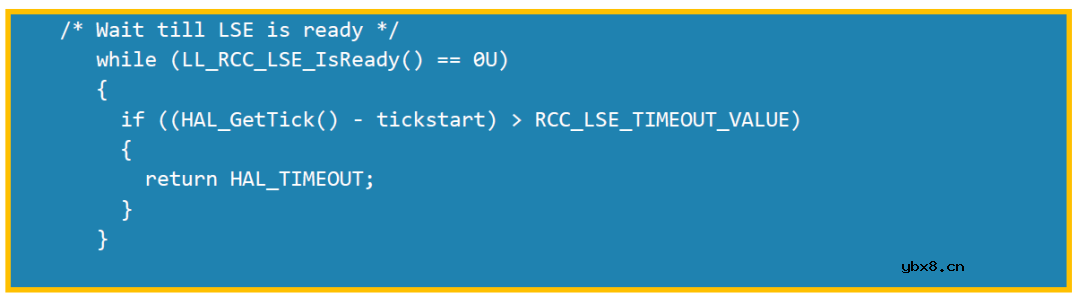

关于STM32WL LSE 添加反馈电阻后无法起振的...

关于STM32WL LSE 添加反馈电阻后无法起振的...

时间:2026-03-05

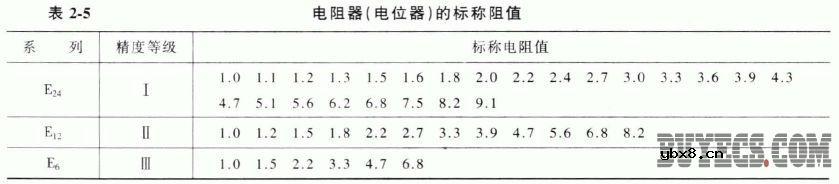

电阻的标称阻值和允许偏差

电阻的标称阻值和允许偏差

时间:2026-03-05

告诉你电容器那些鲜为人知的秘密

告诉你电容器那些鲜为人知的秘密

时间:2026-03-05

3PEAK高压零漂放大器契合精密应用

3PEAK高压零漂放大器契合精密应用

时间:2026-03-05

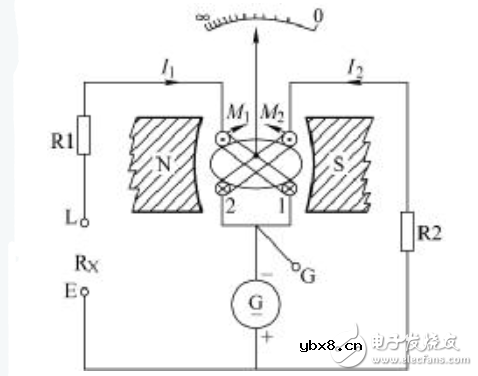

绝缘电阻表原理_绝缘电阻表的作用

绝缘电阻表原理_绝缘电阻表的作用

时间:2026-03-05

绝缘电阻用什么来测量_绝缘电阻测量方法

绝缘电阻用什么来测量_绝缘电阻测量方法

时间:2026-03-05

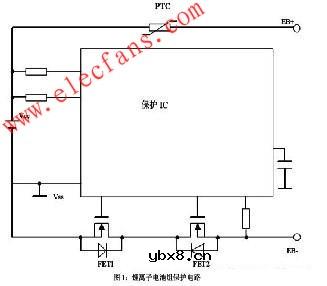

PPTC热敏电阻在电池中的应用

PPTC热敏电阻在电池中的应用

时间:2026-03-05

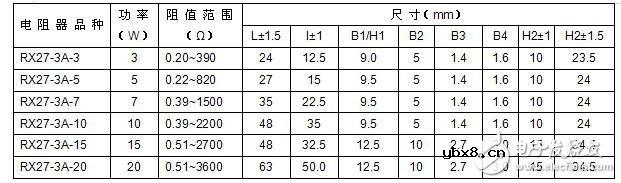

水泥电阻规格及型号

水泥电阻规格及型号

时间:2026-03-05

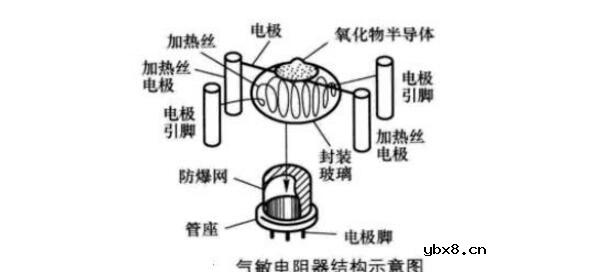

气敏电阻的型号命名方法是怎样的

气敏电阻的型号命名方法是怎样的

时间:2026-03-05

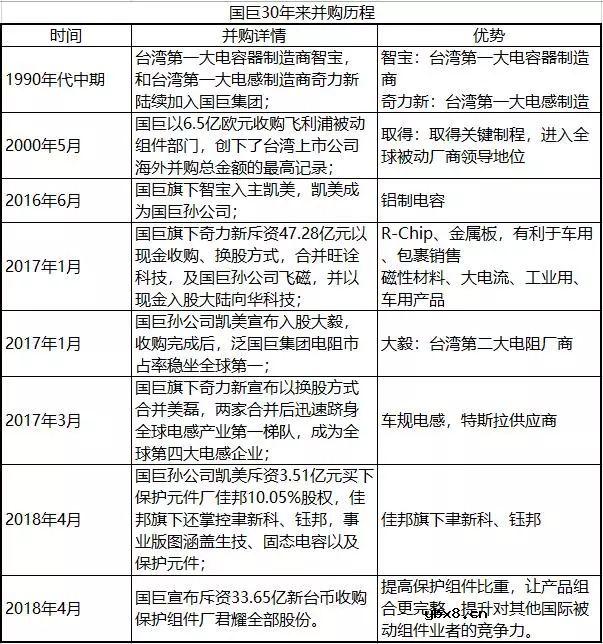

国巨片式电阻缺货涨价之应对方案 你要知道电...

国巨片式电阻缺货涨价之应对方案 你要知道电...

时间:2026-03-05