1 概述

QAMi5516是STMicro(意法半导体)公司最新推出的一款专门针对中低端市场的高性价比数字有线电视(DVB-C)机顶盒单芯片,同时也是ST推出的第一个将前端QAM(正交幅度调制)数字有线信号解调器与后端MPEG视频解码集成在一起的芯片,因而能够很好的使模拟电视用户收看数字有线电视节目。

除了传统的音频、视频解码功能以外,QA-Mi5516还具有很强的扩展能力、增强型图形处理功能和提高音视频质量的后处理功能。同时,由于将QAM解调器和MPEG解码器集成在了一起,因而降低了硬件芯片组的成本,简化了电路设计,提高了产品的可靠性和性价比,也有助于降低生产成本,这对有着近一亿个有线电视家庭用户的中国机顶盒市场来说无疑具有重要意义。

2 功能特点

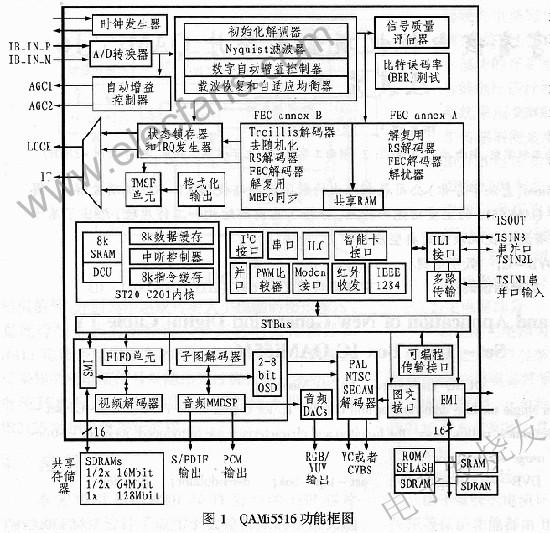

QAMi5516是一款高集成度、高性价比的解调解码单芯片,它内部集成了32位ST20 CPU 、QAM解调器、音频/视频MPEG-2 译码器、显示及图像处理功能和各种系统外设接口等。除了具有数字有线电视机顶盒的全部基本功能外,它还可以运行中间件以实现数字电视营运商的增值服务,同时具有以太网接口、USB接口等丰富的外设接口,从而不仅为实现增值服务建立了很好的硬件环境,而且也能够满足用户上网浏览、电子商务以及电子节目指南等方面的需求。图1 QAMi5516的基本特点如下:

●符合ITU-T J.83 Annexes A/B/C、DVB-C标准;

●支持TSMF;

●集成有QAM解调器,可支持16、32、64、128和256QAM等不同调制方式的解调;

●集成有MPEG-2 MP@ML视频译码器、

●支持时钟可编程;

●功耗低;

●支持两层PCB布板设计;

●采用PBGA封装形式,416引脚。

3 内部结构原理

图1是QAMi5516内部功能框图。现将QA-Mi5516中各主要模块工作原理作以介绍。

3.1 高性能的CPU

QAMi5516中的ST20-C201 CPU内核由ST20C2+CPU、一个用于实时调试的诊断控制器单元(DCU)、内部存储器(8kB SRAM、8kB指令缓存、8kB数据缓存)和一个16级中断控制器组成。其中,ST20C2+CPU是高性能的32位增强型RISC CPU,主频高达180MHz。DCU用于引导CPU,并通过符合IEEE1194.1标准的测试访问端口?Test Access Port?TAP 来实现对所有片上系统的监控。DCU内部带有在线仿真单元(ICE)和逻辑状态分析单元(LSA),可支持软件的实时跟踪调试。对于中断,用中断级控制器(ILC)可将38个中断源映射到中断控制器的16个可编程中断级输入端,并可由软件来控制和改变,在所有16级中断中,第15级优先级最高,第0级优先级最低。

3.2 外部存储器及其接口

QAMi5516的外存可通过外部存储器接口(EMI)来进行扩展,其工作频率最高达100MHz,并支持1GB的地址空间,这对于嵌入式系统来说已经足够了。整个存储地址空间分为四个区域,区域0映射到片内SRAM,区域1映射到片外SDRAM(通过SMI接口扩展),区域2映射到片内外围设备寄存器,区域3映射到外部存储器(通过EMI接口扩展)。其中区域3又分为6个大小可编程设置的BANK,最大为256MB,最小为4MB。表1是该区域的典型配置方式。

3.3 QAM解调器

QAM解调器全面兼容I-TU-T J.83 Annexes A/B/C和DVB-C标准,支持16、32、64、128和256QAM等不同调制方式的解调。对于日本DBS系统,它还能够对TSMF进行后处理,以从多路帧中提取单独的传输流(TS)。

QAMi5516解调器内部集成有一个高性能的模-数转换器,可以直接处理从调谐器出来的中频信号(包括7.2 MHz、36 MHz和44 MHz,最高达57MHz)。另外,还带有用于调谐器增益控制和中频增益控制的数字AGC等,并可降低QAM调制比特流恢复的比特误码率(BER)。

3.4 STBus互连总线

为了改善芯片内部数据传输总线瓶颈问题,QAMi5516采用基于OMEGA2 (奥米加)技术的高速先进的STBus来实现互联。OMEGA2能够为各个模块之间的数据传输提供较高的片上带宽和较低的访问延迟,其多路路由器允许多模块之间进行同步读和写,这样使得有效带宽得到最大的使用率。

3.5 MPEG视频解码器

MPEG视频解码器用于MPEG2比特流的解压缩和视频流的构建,它实际上是通过对一副副图片(画面)进行解码来实现的。一般来说,在新画面显示的同时,下一副画面就已开始插入相应的启动代码检测器,这样CPU就可以自动设置相应的寄存器对下一副画面进行解码。此外,该视频解码器还包括MPEG子图解码器、图像显示单元及OSD单元,而其多层显示功能也大大丰富了电视显示效果。

3.6 数字编码器

数字编码器用于将4:2:2的数字视频流转换成标准的PAL/SECAM/NTSC模拟基带信号,也可以将4:4:4的数字视频流转换为RGB和YUV信号。它提供有6路模拟输出,可以支持S-VHS(Y/C)+CVBS+RGB、S-VHS(Y/C)+CVBS+YUV、Y1+C1+CVBS1+C2+Y2+CVBS2等三种组合输出方式。此外,QAMi5516内部还集成有音频子系统、调制解调器、时钟发生器等单元模块,还有智能卡接口、异步串口、I2C收发器以及IEEE1284增强型高速并口等片内外设接口。

在应用设计中,要充分考虑到芯片的性能要求和极限参数,表2给出了QAMi5516的主要参数。

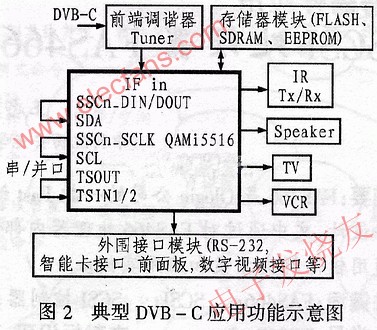

图2是一个基于QAMi5516的典型DVB-C数字有线电视机顶盒的功能示意图。当DVB-C有线电视网利用同轴电缆传送的数字电视射频信号(频率范围为50MHz~870MHz)送到前端调谐器(Tuner)后,该信号会变换为一个中心频率为43.75MHz的中频信号,并通过IF in输入到QAMi5516内部的QAM解调器,以完成信号的定时恢复、载波恢复、数据成型、自适应均衡和维特比解码(Viterbi,又叫格形解码)、解交织、RS解码和去随机化,最后将得到的符合MPEG-2标准的传输流经过TSOUT串/并口输出。这样就完成了整个信道解码。显然,这部分功能主要是由硬件来完成的,软件只需对相应的寄存器进行初始化和控制。

从TSOUT输出的MPEG-2传输流又将从TSIN1/2送到信源解码模块以进行解复用、视频解码和音频解码;然后再经过PAL/SECAM /NTSCS视频编码器、音频DAC等处理模块,就可以输出相应格式的音视频信号了。

存储器模块主要包括FLASH、EEPROM和SDRAM等。其中FLASH用于存放用户应用程序,EEPROM用于存放系统、用户配置信息以及所有的节目信息,SDRAM是系统和应用程序运行的地方,而视频SDRAM则用作视频解码缓冲区以存放OSD数据。

外围接口模块包括与外界的接口及控制电路。其中RS-232和RJ45网络接口用于系统和主机的数据传输,也可用于系统软件升级和机顶盒故障诊断。前面板和遥控接口用于接收前面板和遥控器的输入。智能卡接口用于支持CA有条件访问控制系统,该接口符合ISO7816-3国际标准。此外,JTAG接口用于软件调试和下载。

在工程设计中,对芯片操作系统的选取也是至关重要的,但这方面较易被忽视。事实上,操作系统往往会对系统的开发时间、难度和整机价格起到相当大的作用。ST在其配套的软件开发包中带有专门针对ST20内核优化的专用嵌入式操作系统STLite/OS20,因而可大大减轻软件程序员的工作。

5 结束语

为了尽可能地最小化设计成本,加速数字电视机顶盒的开发速度,ST在推出QAMi5516的同时,还提供了完整的设计支持,包括电路设计方案、