2006年,美国国家半导体创新地研发出单对双绞线差分传输的串行解串器(SerDer)FPD-Link II 芯片组系列,这种串行化方案由于消除了在数据和时钟路径间的偏斜,简化了在单一个差动对上转换24位总线的工作。通过单对双绞线,可有助削减PCB的层数、缆线宽度以及连接器的尺寸和管脚,从而节省系统成本。

在传统的显示系统设计中,绘图控制器或绘图处理器(GPU)会传送有像素时钟和同步信号对齐的并行RGB颜色位,这些信号使用TTL电平,信号线有二十多条,在远程的LCD显示器连接中,有时会因缆线太厚,或者电源和EMC(电磁兼容性)等问题而导致并行总线不能超过20cm~30cm的长度。

为解决这个问题,美国国家半导体在90年代的中期与当时领导业界的TFT面板供货商一起研发了串行解串器(SerDes)FPD-Link(平面显示器-链接)芯片组系列。该传送器收集高至18位/24位的RGB信息(6位/8位色彩)以及三个控制信号和时钟,然后将它们转换成三个差动数据对和一个时钟对。线对减小到4对,使用LVDS传输,以解决EMC问题。是笔记本电脑\液晶显示器\液晶电视的显示屏接口标准。

DS90UR241/124的功能

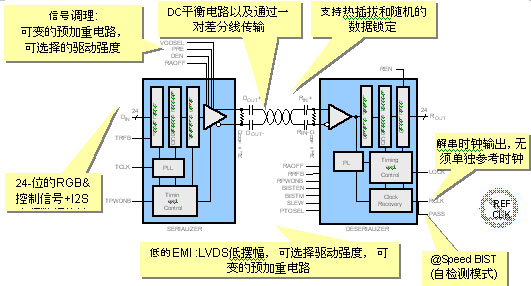

DS90UR241/124芯片组是5-43MHz DC平衡的24位LVDS串行化器/并行化器,具有24:1和1:24的数据传输,具有用户定义的预加重,支持AC耦合的数据传输,嵌入了时钟和数据恢复(CDR),电源电压3.3V ± 10%,具有广泛的用途。主要特点:一对差分双绞线传输,布线简单,成本低;24位数据串化/解串(18位的视频+控制信号+I2S的音频);信号调理电路可将传输延长至10米,满足长距离传输要求;非常低的EMI,容易通过车规测试;数据中嵌入时钟,使得解串器端不需要参考时钟,减少系统成本;内建BIST模式(方便进行工厂测试/在线诊断);通过AEC-Q100 2级(汽车级认证资格)。

DS90UR241/DS90UR124在汽车显示系统中的应用

汽车显示系统的应用包括:中控台的显示,后坐头枕显示,汽车仪表显示,导航系统显示。其他的如:平视显示系统,后视显示系统,摄像系统/传感系统/其他的辅助驾驶系统。

一般的WVGA格式的显示屏采用800×480 WVGA分辨率,18位(色深,RGB666格式),时钟频率30MHz左右。

图1:FPD-Link II DS90UR241/124功能框图。

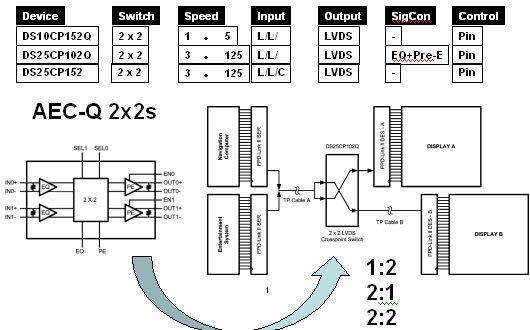

图2:FPD-Link II显示信号切换应用(交叉开关)。