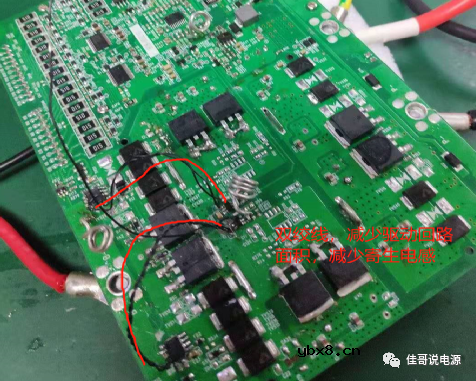

下图是一款DCDC电源初样,测试时发现上电,或带大载时出现炸机,示波器测试驱动IC输入端

波形,发现严重振荡,检查PCBlayout,发现驱动走线回路与功率回路出现交叉,且由于考虑到

过认证,打静电和EFT,使得GPS MCU等数字地线和驱动地线,选通IC地都接到电池地 ,按照通常的反激电源

layout经验走线 使得选通IC到驱动IC走线环路面积非常大;后割断原来走线,用双绞线代替原来走线,

再也没出现炸机情况

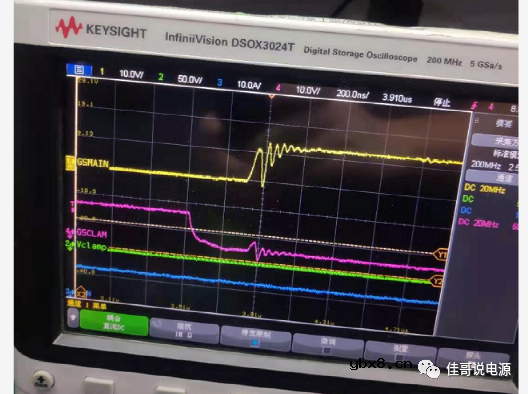

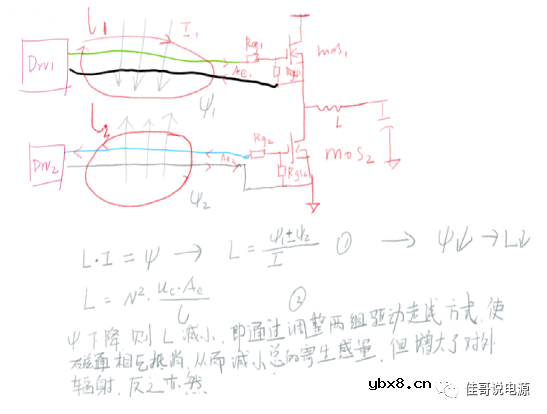

下面从理论简易分析为什么减少回路面积可以减少驱动振荡?

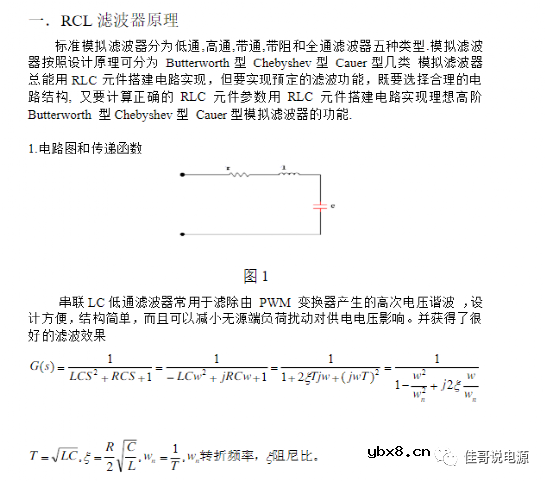

MOS驱动回路可等效为RCL二阶振荡模型

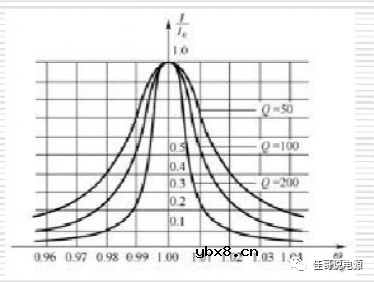

对于一定开关频率,减小Q值,则可以减少振荡时电压幅值,如何减少Q值?

1、减少L 2、增大C 3、增大R 在后续仿真加以验证

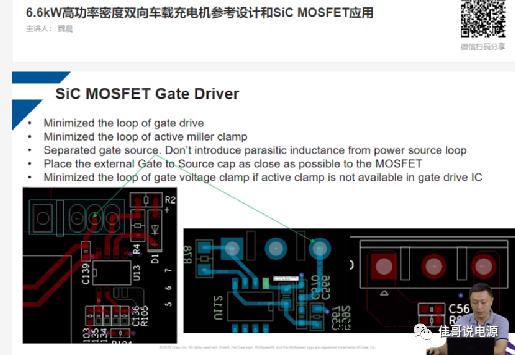

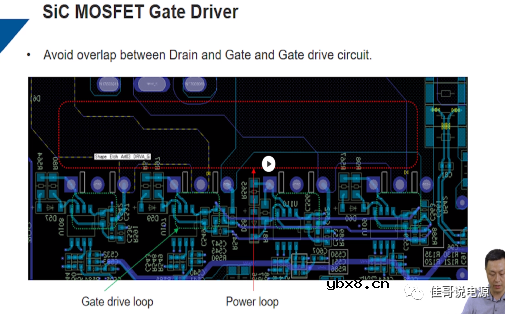

驱动电路PCBlayout要点:

1、避免驱动回路与功率回路重叠,

一方面重叠会增加功率回路与驱动

回路寄生耦合电容面积,另一方面增加了

耦合磁路面积

2、减少驱动回路面积;就近GS放置电容;分离

驱动回路source极和功率回路source极

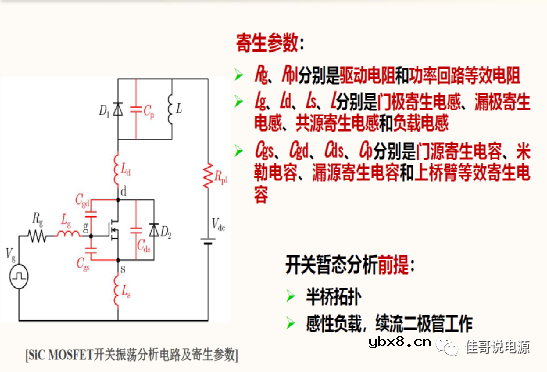

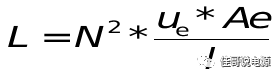

如何减少寄生电感?

L:自感感量

N:电感匝数

:相对磁导率

Ae:磁路等效截面积

u:磁导率

l:磁路等效路径长度

由上述电感计算公式可知:减少寄生电感方法有 (对于驱动回路匝数N为1)

1:减少相对磁导率

2:减少回路面积

3:增加磁路长度

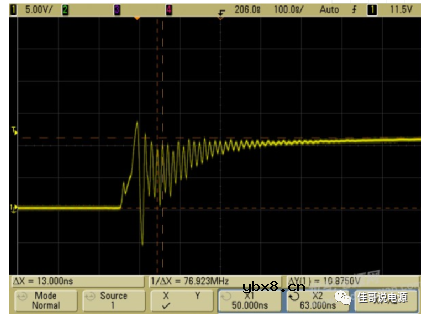

在实际PCB Layout中 ,驱动电路通过差分对走线的方式减少驱动回路面积

如下图,则可通过走差分对尽量的形式,减少驱动回路Ae面积,同时驱动IC的地线与MOS管source极直接相连

另外对于半桥而言DRV1与DRV2驱动时序刚好相差180度,也即磁通方向刚好反向可运用空间耦合方式减少等效磁导率从而减小寄生电感,反之可以降低对外辐射。

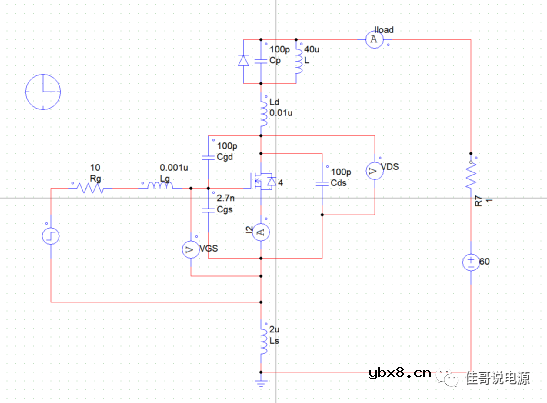

仿真原理图如下 软件平台:PSIM 9.04

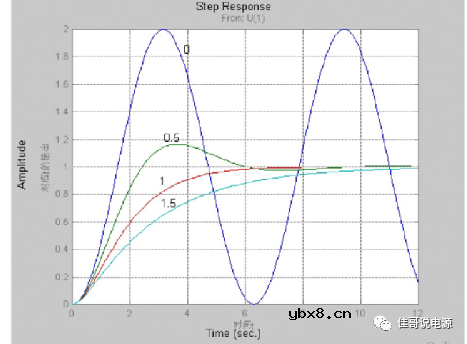

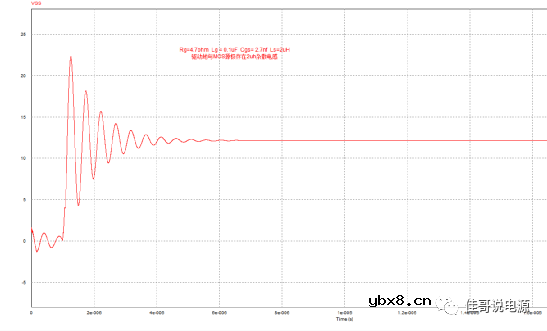

实际仿真

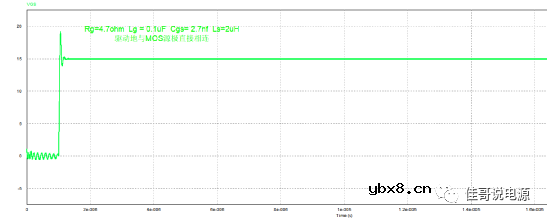

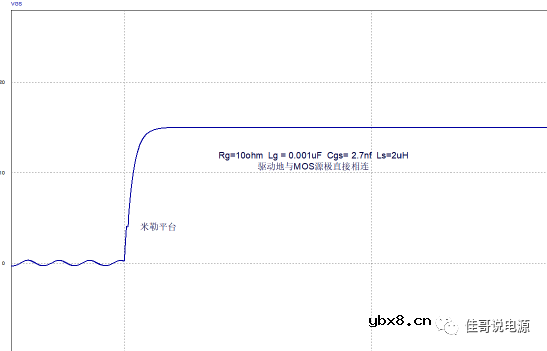

与图一相比,只是将驱动的source与mos的source直接相连,振荡明显减小

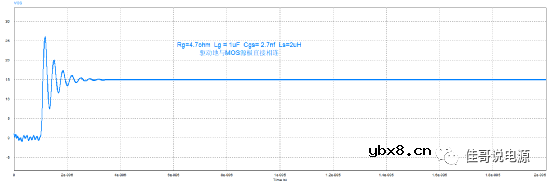

与图二相比,将驱动回路杂散电感由0.1uH增大到1uH,振荡加剧

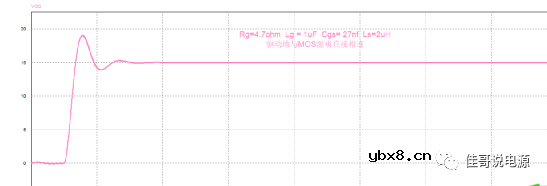

与图三相比,增加GS电容到27nf,振荡减小

将Rg增大到10ohm,驱动回路寄生电感减少到0.001uH后,振荡消失

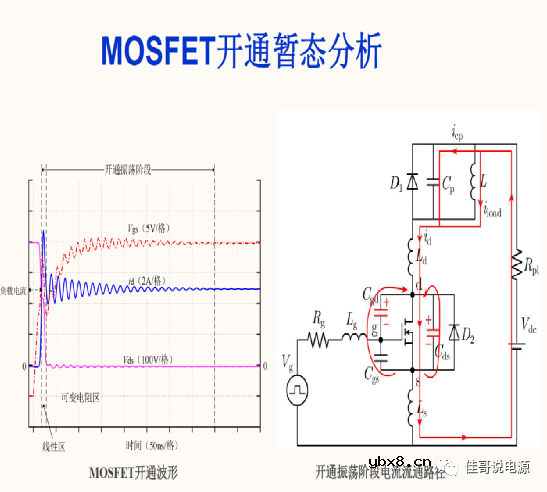

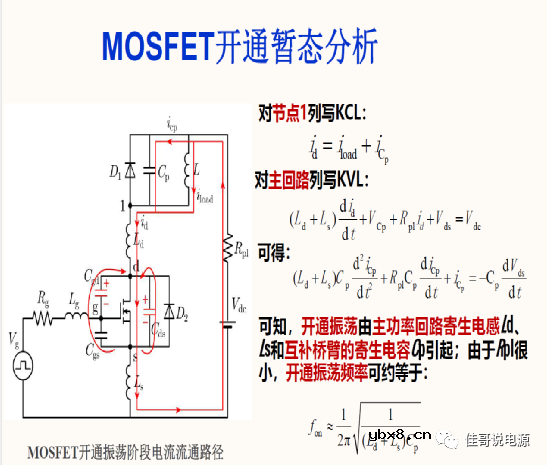

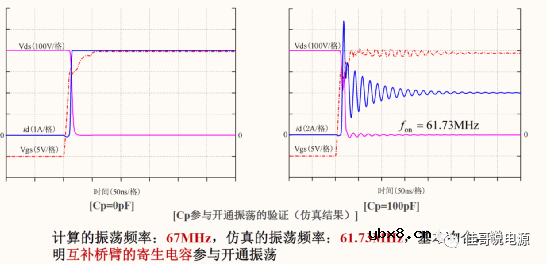

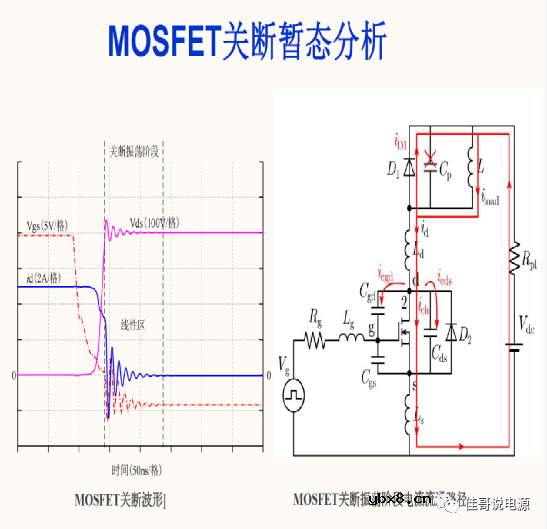

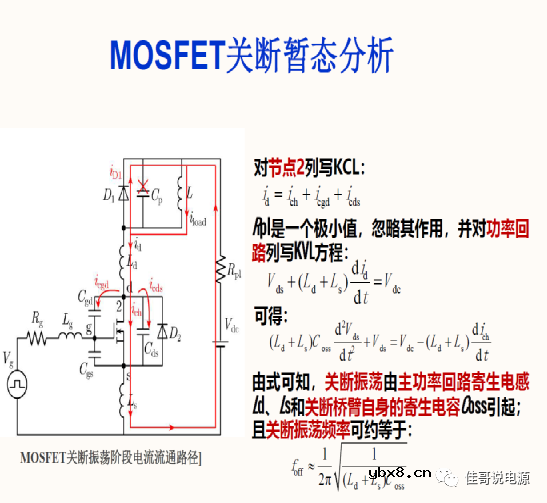

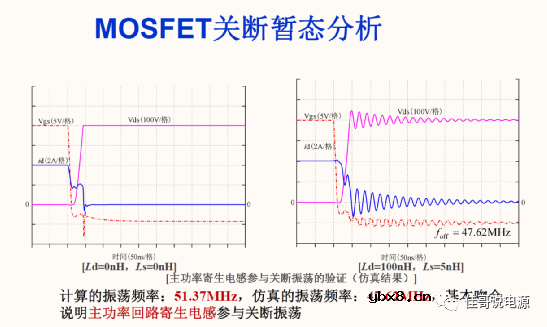

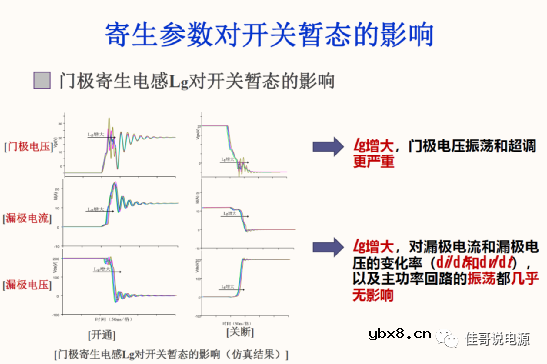

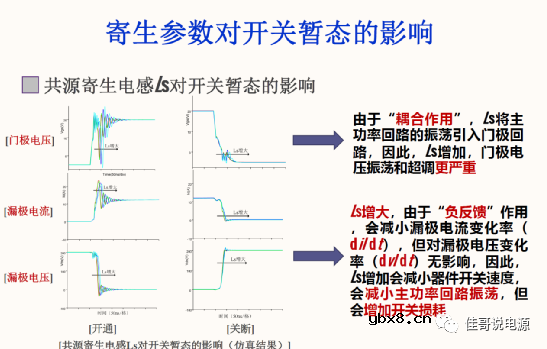

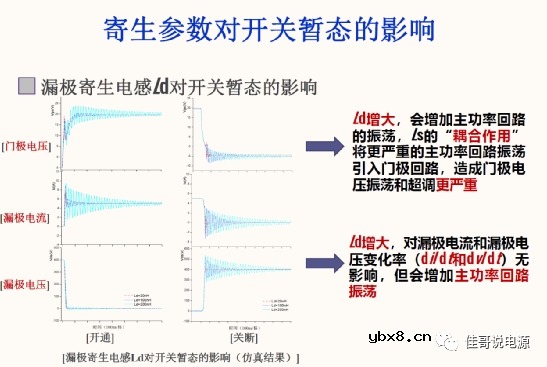

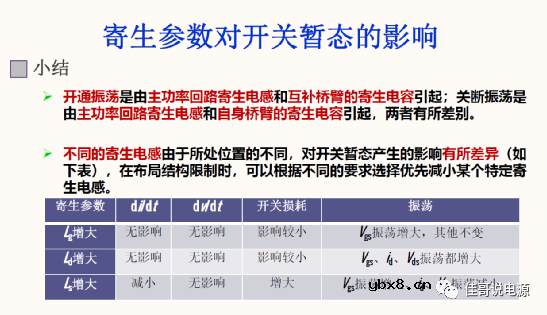

MOSFET开关暂态分析

microBUCK® 同步降压稳压器获中国人工智能...

microBUCK® 同步降压稳压器获中国人工智能...

时间:2026-03-12

超薄MTC封装130A~300A三相桥式功率模块具有...

超薄MTC封装130A~300A三相桥式功率模块具有...

时间:2026-03-12

如何学好单片机?

如何学好单片机?

时间:2026-03-12

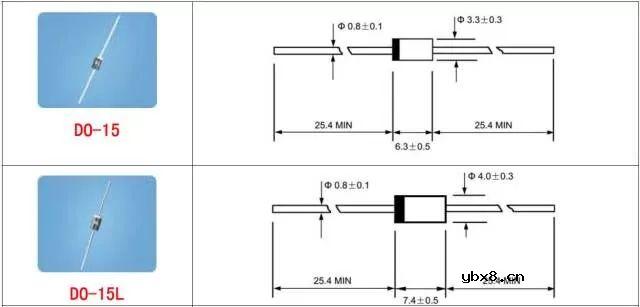

总结了60种硬件工程师常用封装实物图

总结了60种硬件工程师常用封装实物图

时间:2026-03-12

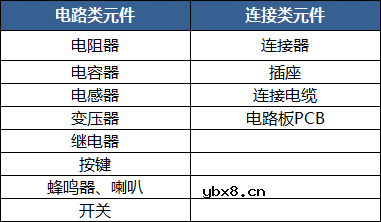

常用电子元器件的划分与识别

常用电子元器件的划分与识别

时间:2026-03-12

脑机接口最新科研进展,以“半侵入性”方式...

脑机接口最新科研进展,以“半侵入性”方式...

时间:2026-03-12

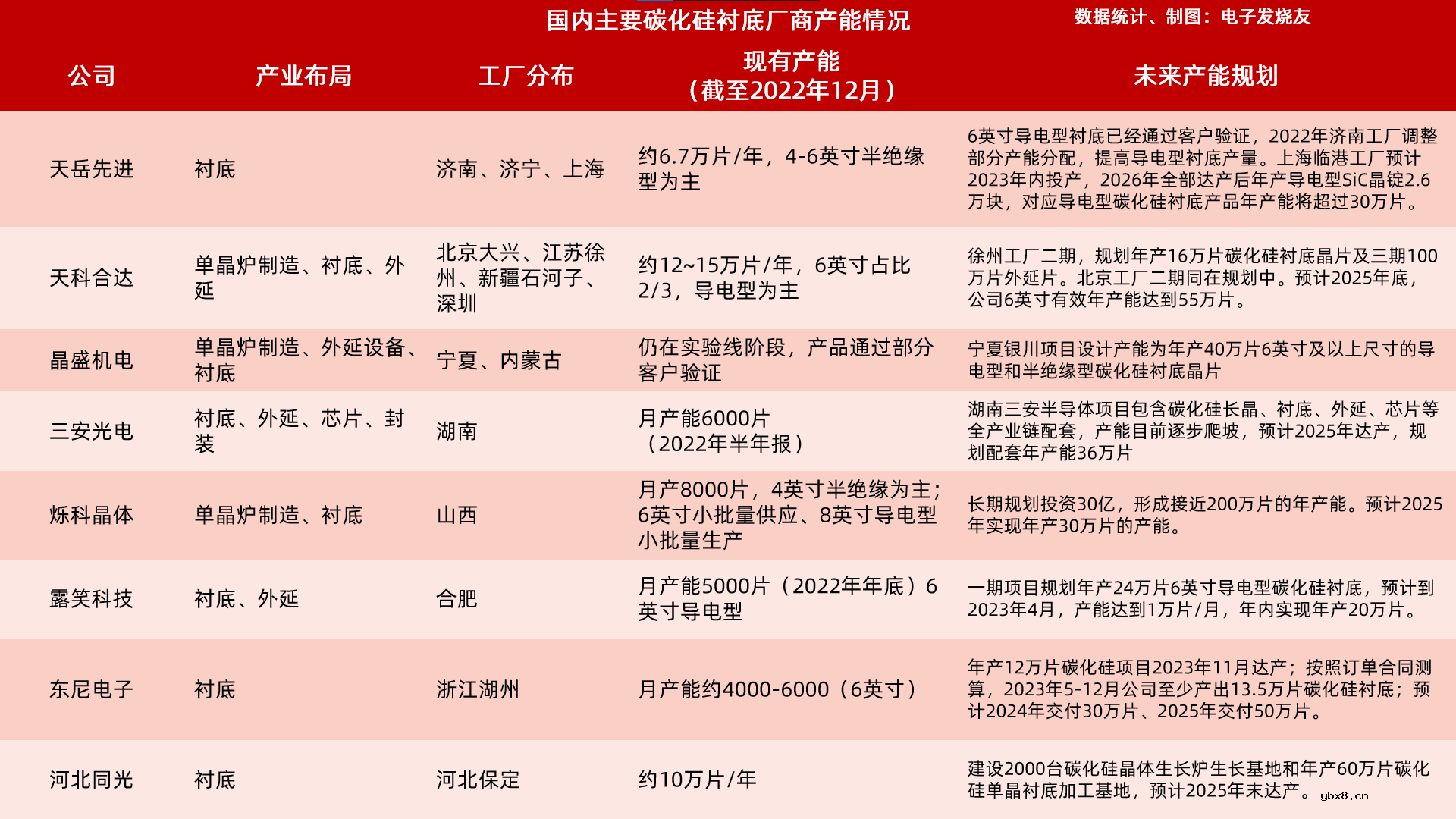

国内主要碳化硅衬底供应商产能分析,与海外...

国内主要碳化硅衬底供应商产能分析,与海外...

时间:2026-03-12

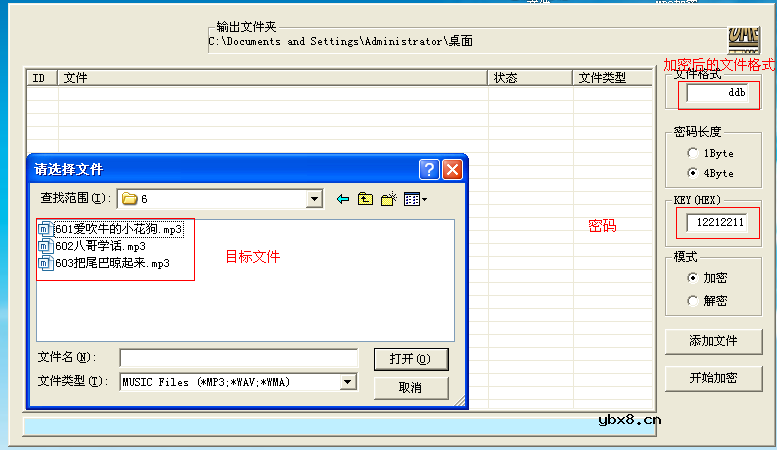

KT1025A双模蓝牙音频文件加密说明

KT1025A双模蓝牙音频文件加密说明

时间:2026-03-12

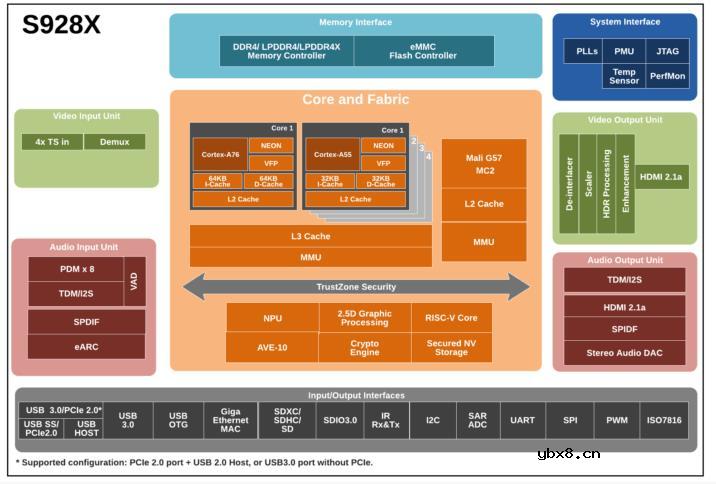

晶晨半导体8K智能机顶盒SoC芯片S928X特性解...

晶晨半导体8K智能机顶盒SoC芯片S928X特性解...

时间:2026-03-12

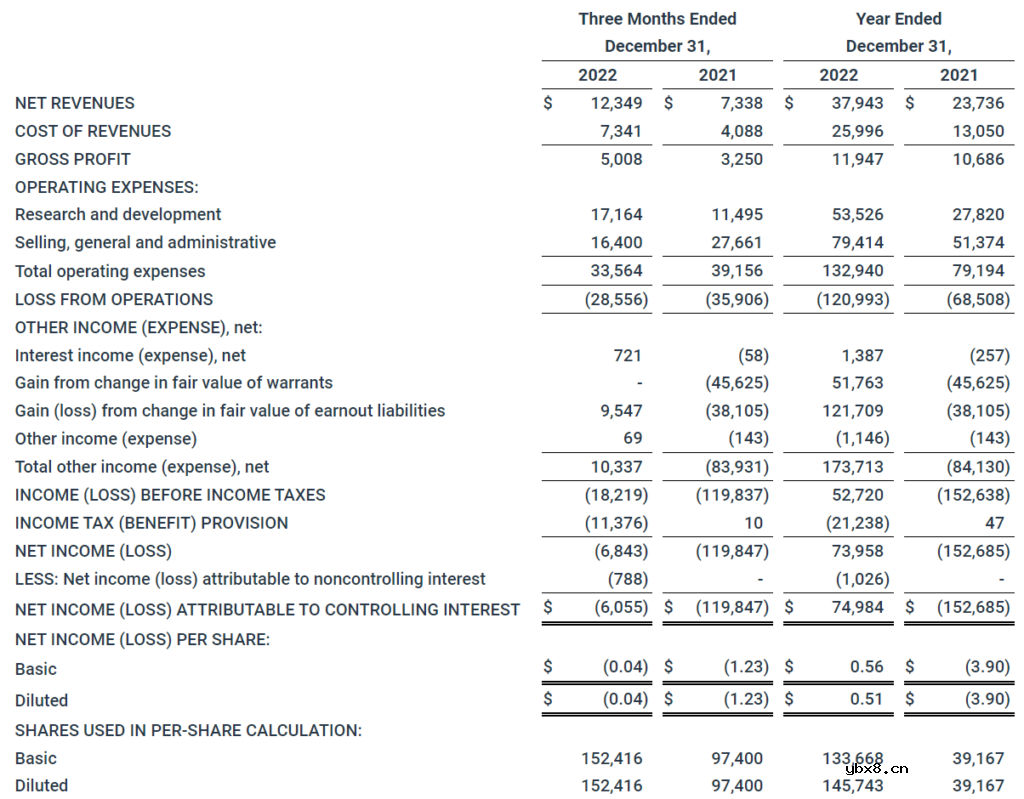

纳微半导体2022年第四季度及全年财报亮眼 ...

纳微半导体2022年第四季度及全年财报亮眼 ...

时间:2026-03-12

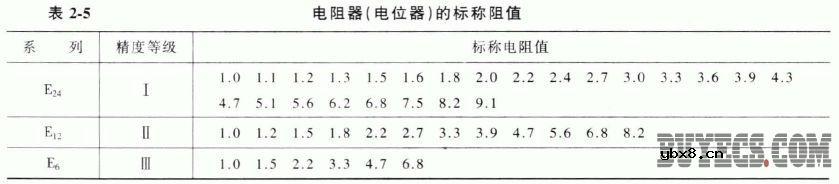

电阻的标称阻值和允许偏差

电阻的标称阻值和允许偏差

时间:2026-03-05

玻璃釉电容器的结构与特点

玻璃釉电容器的结构与特点

时间:2026-03-05

压敏电阻有正负极吗

压敏电阻有正负极吗

时间:2026-03-05

变压器并列运行的条件浅析

变压器并列运行的条件浅析

时间:2026-03-06

电容器入门教程

电容器入门教程

时间:2026-03-05

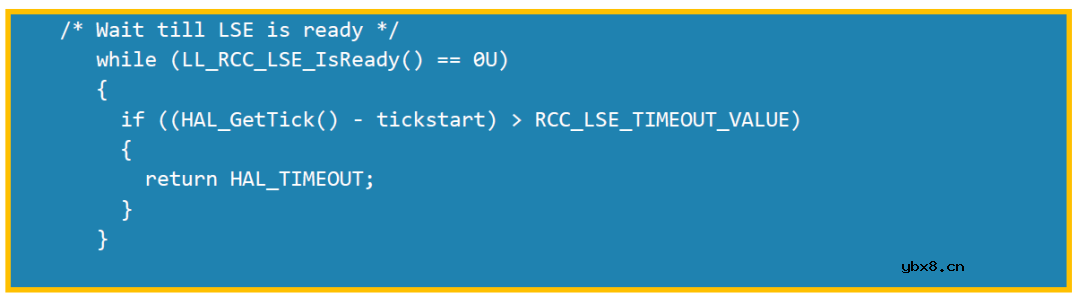

关于STM32WL LSE 添加反馈电阻后无法起振的...

关于STM32WL LSE 添加反馈电阻后无法起振的...

时间:2026-03-05

可调电阻怎么接线

可调电阻怎么接线

时间:2026-03-05

压敏电阻坏了怎么替代

压敏电阻坏了怎么替代

时间:2026-03-05

压敏电阻爆裂的原因分析

压敏电阻爆裂的原因分析

时间:2026-03-05

暑期买元器件下单立减还送华为P30pro

暑期买元器件下单立减还送华为P30pro

时间:2026-03-05